# basic education

Department:

Basic Education

REPUBLIC OF SOUTH AFRICA

# NATIONAL SENIOR CERTIFICATE

**GRADE 12**

**ELECTRICAL TECHNOLOGY: DIGITAL**

**NOVEMBER 2019**

**MARKING GUIDELINES**

**MARKS: 200**

These marking guidelines consist of 16 pages.

# **INSTRUCTIONS TO THE MARKERS**

- 1. All questions with multiple answers imply that any relevant, acceptable answer should be considered.

- 2. Calculations:

- 2.1 All calculations must show the formulae.

- 2.2 Substitution of values must be done correctly.

- 2.3 All answers MUST contain the correct unit to be considered.

- 2.4 Alternative methods must be considered, provided that the correct answer is obtained.

- 2.5 Where an incorrect answer could be carried over to the next step, the first answer will be deemed incorrect. However, should the incorrect answer be carried over correctly, the marker has to recalculate the values, using the incorrect answer from the first calculation. If correctly used, the candidate should receive the full marks for subsequent calculations.

- 2.6 Markers should consider when and where a candidate has rounded off in a calculation, as well as the subsequent effect it has on the final answer obtained. The calculation should therefore be awarded marks on merit.

- 3. These marking guidelines are only a guide with model answers. Alternative interpretations must be considered and marked on merit. However, this principle should be applied consistently throughout the marking session at ALL marking centres.

# **QUESTION 1: OCCUPATIONAL HEALTH AND SAFETY**

| 1.1 | <ul><li>Tea</li><li>Tea</li><li>Wo</li></ul>                        | An employee with a sense of teamwork helps a team to meet its goals.  Teamwork helps a team deliver quality work. ✓  Teamwork can win the respect of your co-workers.  Working together as a team can improve discipline in the workshop.  Teamwork will lead to improved productivity.                                                                                                                    |             |  |

|-----|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| 1.2 | 1.2.1                                                               | <ul> <li>The purpose of the Act is to:</li> <li>Provide for health and safety of persons at work. ✓</li> <li>Protect against hazards arising from the activities of other people at work. ✓</li> <li>Establish an advisory council for occupational health and safety and related matters.</li> <li>Provide for health and safety for persons in connection with the use of plant and machinery</li> </ul> | (2)         |  |

|     | 1.2.2                                                               | Workplace can be defined as any premises or place where a person performs work ✓ during the time of his employment. ✓                                                                                                                                                                                                                                                                                      | (2)         |  |

| 1.3 | 1.3.1                                                               | Employee. ✓ Learner, Supervisor, Team leader, Safety representative                                                                                                                                                                                                                                                                                                                                        | (1)         |  |

|     | 1.3.2                                                               | Health and safety representative. ✓ Inspector.                                                                                                                                                                                                                                                                                                                                                             | (1)         |  |

| 1.4 | <ul><li>Std</li><li>Sw</li><li>No</li><li>If t</li><li>Mo</li></ul> | emain calm.  op whatever you are doing.  vitch off machinery.  otify a responsible adult or teacher.  here is an emergency stop nearby activate it if necessary.  ve in an orderly manner to the nearest assembly point.  responsible adult or teacher.                                                                                                                                                    | (2)<br>[10] |  |

|     |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                            |             |  |

## **QUESTION 2: SWITCHING CIRCUITS (GENERIC)**

2.1 2.1.1 A – Bistable multivibrator ✓

B – Monostable multivibrator ✓

(2)

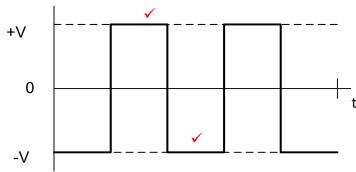

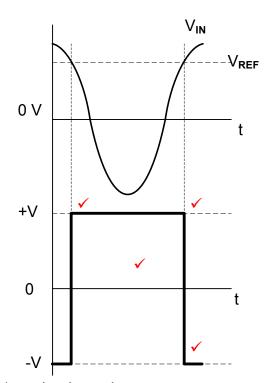

2.1.2

2 marks = 1 mark for each correct half cycle

If waveform is correctly drawn but inverted, 2 marks will be awarded

**NOTE:** Due to the +V instead of -V typo on the answer sheet, the following responses are also accepted.

(2)

2.2 2.2.1 Resistors R₁ and R₂ are pull-up resistors. ✓ ✓

Resistors R₁ and R₂ will hold both trigger pin 2 and reset pin 4 high.

(2)

2.2.2 Trigger pin 2 will be pulled low ✓ and cause the IC output to 'flip' and rise high ✓ turning the LED on ✓ When set switch S₁ is pressed,

(3)

2.2.3 Threshold pin 6 is purposely held at 0 V ✓ causing the IC not to reset, ✓ keeping the output high ✓ when S₁ is pressed.

(3)

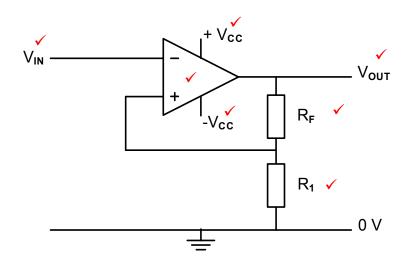

2.3 2.3.1 The output signal represents an inverting Schmitt trigger ✓ because the output signal is inverted ✓ with reference to the input signal. ✓

OR

The output signal is at  $-V_{CC}$  when triggered by the upper trigger voltage and swings to  $+V_{CC}$  when triggered by the lower trigger voltage.

(3)

2.3.2

**NOTE:** Where a portion of the circuit is incorrect, the learner will lose those marks and will be awarded marks for the correct section / labels.

Any 7 correct labels (7)

2.4 2.4.1 Inverting ✓ comparator ✓

(2)

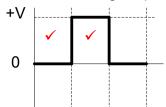

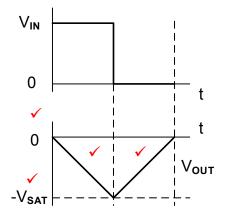

2.4.2

1 mark = inversion

1 mark = correct wave shape

2 marks = 1 mark for each correct trigger point.

(4)

(2)

- 2.4.3 Change the connection of resistor R₁ ✓ from the positive supply to the negative supply. ✓

- 2.5 2.5.1 The gain of the amplifier is determined by the ratio ✓ of the feedback resistance ✓ to the input resistance of each branch. ✓ **NOTE:** Writing the formula only = 1 mark.

(3)

2.5.2

$$V_{OUT} = -\left(V_1 \frac{R_F}{R_1} + V_2 \frac{R_F}{R_2} + V_3 \frac{R_F}{R_3}\right)$$

$$= -\left(0.3 \times \frac{100 \times 10^3}{20 \times 10^3} + 0.5 \times \frac{100 \times 10^3}{20 \times 10^3} + 0.4 \times \frac{100 \times 10^3}{20 \times 10^3}\right) \checkmark$$

$$= -6 \text{ V}$$

**NOTE:** If the – sign is omitted in the answer, it is incorrect because it is an inverting summing amplifier. (3)

2.5.3 The amplifier is not saturated because the output voltage is less ✓ than the supply voltage. ✓ (2)

2.5.4

$$V_{OUT} = V_{IN} \times Gain$$

$$Gain A_{V} = \frac{V_{OUT}}{V_{IN}}$$

$$= \frac{V_{OUT}}{(V_{1} + V_{2} + V_{3})}$$

$$= \frac{-6}{(0,3 + 0,5 + 0,4)}$$

$$= -5$$

(3)

- 2.5.5 With a variable resistor in the feedback loop, the gain ✓ of the amplifier can be varied / controlled. ✓ (2)

- 2.5.6 If  $R_2$  is changed to 10 kΩ, the gain for  $V_2$  will increase  $\checkmark$  causing the total output voltage to increase.  $\checkmark$  (2)

- 2.6 2.6.1 RC passive ✓ differentiator ✓

NOTE: RC circuit = 1mark (2)

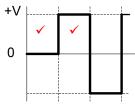

2.6.2

Input

Output

Outpu

1 mark = positive pulse

1 mark = negative pulse

1 mark = correct orientation (3)

2.6.3 If the circuit time constant is increased, the capacitor will discharge slower ✓ producing a sagging square wave. ✓

**NOTE:** If the learner draws the waveform and label correctly, mark on merit.

2.7 2.7.1 C<sub>F</sub> provides a feedback connection from output to input. ✓ (1)

2.7.2 The inputs draw zero current. ✓

The two inputs possess the same voltage at all times. ✓

The capacitor will charge at a constant rate when a constant current is supplied. ✓

**NOTE:** If the learner gives a correct account of the operation of the integrator as applied with the 741 op-amp, the answer must be marked on merit.

(3)

(2)

2.7.3

2 marks = correct labelling

2 marks = 1 mark for each correct half cycle

**NOTE:** The wave must be drawn correct before marks can be awarded for labelling.

(4)

[60]

#### **QUESTION 3: SEMICONDUCTOR DEVICES**

3.1 Pin 1 is identified by being the first pin to the left and below the indentation. ✓

**OR**

Being closest to the dot in the body.

(1)

3.1.2 Input stage ✓ or differential amplifier

Intermediate stage ✓ or high gain differential amplifier

Output stage ✓ or common collector

(3)

(2)

3.1.3 • It stabilises the amplifier. ✓

Distortion of the output signal is reduced. ✓

The bandwidth increases.

3.2 3.2.1

$$V_{OUT} = V_{IN} \times \left( -\frac{R_F}{R_{IN}} \right)$$

$$= 2 \times \left( -\frac{100 \times 10^3}{12 \times 10^3} \right)$$

$$= -16.67 \text{ V}$$

(3)

3.2.2 The amplifier is driven into saturation ✓ which causes the tops and bottoms to be clipped. ✓

**NOTE:** If the learner identified that the input is fed into the inverting input, there will be a 180 degree phase shift on the output = 2 marks (2)

3.2.3 +15 volts  $\checkmark$  -15 volts  $\checkmark$  (2)

3.3 3.3.1 Dual in-line ✓ package

(1)

3.3.2 Astable mode ✓

Monostable mode ✓

Bistable mode ✓

(3)

$3.3.3 \quad 5 \, \text{V} \checkmark$

3.4 When the trigger voltage rises above the threshold voltage, the output of a 555 timer will change state ✓ from high to low. ✓

**NOTE:** If the answer is given as "Switch off" only = 1 mark

(2) **[20]**

(6)

# **QUESTION 4: DIGITAL AND SEQUENTIAL DEVICES**

# 4.1 Polarisation ✓ (1)

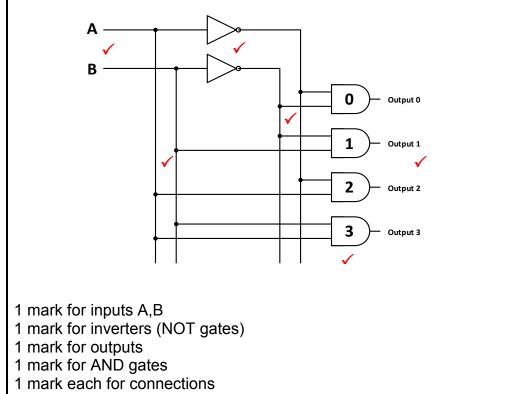

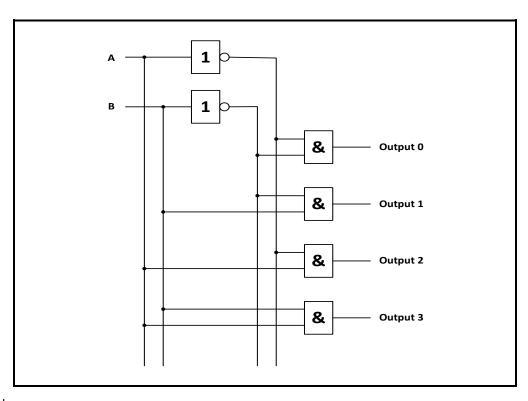

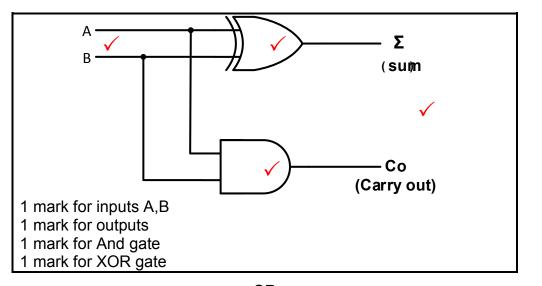

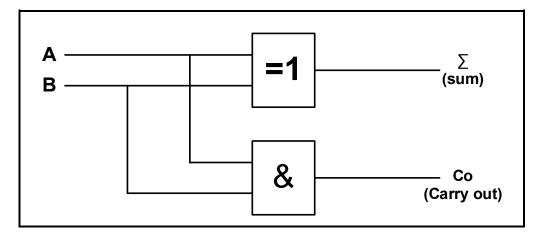

# 4.2 4.2.1

**NOTE:** Where a portion of the circuit is incorrect, he/she will lose those marks and will be awarded marks for the correct section / labels.

OR

(4)

(3)

(4)

(4)

4.2.2

| Inp | outs | Outputs |    |    |     |

|-----|------|---------|----|----|-----|

| Α   | В    | 0       | 1  | 2  | 3   |

| 0   | 0    | 1√      | 0  | 0  | 0   |

| 0   | 1    | 0       | 1√ | 0  | 0   |

| 1   | 0    | 0       | 0  | 1√ | 0   |

| 1   | 1    | 0       | 0  | 0  | 1 ✓ |

**TABLE 4.2.2**

4.3 4.3.1 Clock ✓ (1)

4.3.2 The driver transistors are used to feed each LED in the display separately ✓ to ensure that all bars of a number are illuminated ✓ to the same level. ✓

4.3.3

| Inputs |   |   |   |   |    |   | Outpu | ts |    |   |

|--------|---|---|---|---|----|---|-------|----|----|---|

| Α      | В | С | D | а | b  | С | d     | е  | f  | g |

| 0      | 1 | 0 | 1 | 1 | 0√ | 1 | 1√    | 0√ | 1√ | 1 |

4.4 4.4.1

OR

4.4.2

| INP | UTS | OUTPUTS |     |  |

|-----|-----|---------|-----|--|

| Α   | В   | Σ       | Co  |  |

| 0   | 0   | 0       | 0 🗸 |  |

| 0   | 1   | 1√      | 0   |  |

| 1   | 0   | 1       | 0 🗸 |  |

| 1   | 1   | 0√      | 1   |  |

**TABLE 4.4.2**

(4)

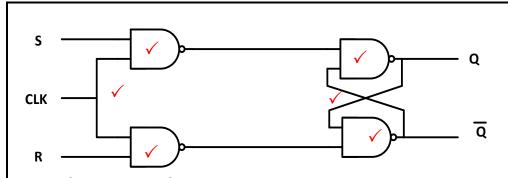

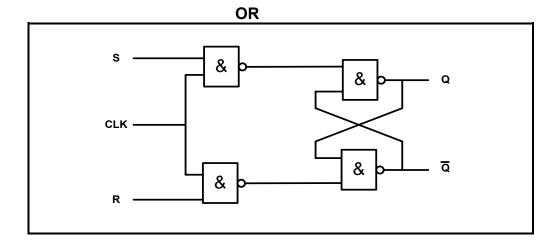

4.5 4.5.1

- 1 mark for input gate S

- 1 mark for input gate R

- 1 mark for output gate Q

- 1 mark for output gate  $\overline{Q}$

- 1 mark for latch

- 1 mark for clock connection

**NOTE:** Where a portion of the circuit is incorrect, the learner will lose those marks and will be awarded marks for the correct section / labels.

(6)

4.5.2

|     | INPUT | OUTPUTS |                                 |     |  |

|-----|-------|---------|---------------------------------|-----|--|

| CLK | S     | R       | $oldsymbol{Q} oldsymbol{ar{Q}}$ |     |  |

| Л   | 0     | 0       | NO CHANGE                       |     |  |

| Л   | 0     | 1       | 0 🗸                             | 1 ✓ |  |

| Л   | 1     | 0       | 1 ✓                             | 0 ✓ |  |

|     | 1     | 1       | INDETERMINATE                   |     |  |

(4)

4.6 Frequency divider ✓

Decade counter ✓

Binary coded decimal (BCD) counter

(2)

- When a logic low '0' is applied to the circuit it has no effect on the JK flip-flop. ✓

- When a logic high is applied to the inputs, the J and K inputs of each stage are held high '1' ✓

- Turning them each into a single stage 'toggle' that will respond to the status of its preceding stage, ✓

- After a clock pulse is only applied on the first flip flop it will change state. ✓

- Going high '1' on the first pulse and low '0' on the next pulse. ✓

- Rather than allow the counter to run through its full count term, a NAND gate is added with its two inputs connected to the outputs of the first and fourth flip-flop. ✓

- Once the count reaches 1001 (decimal 9) the NAND gate's output will trigger low '0' thus activating the 'clear' inputs of each flip-flop, ✓

- Re-setting them all to zero. ✓ and the process repeats itself.

**NOTE:** Although the following statement is wrong, if the learner writes it in the place of the second bullet, a mark must be awarded, because it is wrongly stated in the prescribed textbook

- When a logic high '1' is applied to the circuit it immediately clears or resets the flip-flop back to its original position.

- (8)

4.8 4.8.1 Parallel-in; Serial-out shift register ✓

(1)

4.8.2 A = Clock  $\checkmark$ ,

B = 4-bit Parallel Data Input ✓

B = Input, Parallel Data Input = 1

(2)

- 4.8.3 In the Parallel-in Serial-out shift register all four bits of the data are introduced to the register at the same time in parallel.✓

- (1)

(1)

- 4.8.4 It is shifted out, one bit at a time ✓ controlled by the clock input cycle.

- 4.8.5 The circuit enables parallel data ✓ to be converted ✓ into serial format. ✓

#### OR

The circuit enables parallel data, like an 8-bit word

- · to be converted into serial format, or

- to mix a number of input lines together into a single stream of data

- that can be sent directly to a computer or be transmitted over a communication line.

(3) **[55]**

#### **QUESTION 5: MICROCONTROLLERS**

5.1 A microcontroller is a computer presented in a single integrated circuit ✓ which is dedicated to perform a task/s ✓ and execute one specific application. ✓

### OR

A microcontroller is an independent device, a computer on a chip that can perform a limited range of functions without needing to rely on other chips or devices.

(3)

5.2 5.2.1 First, it fetches instructions and data from memory. ✓ It then decodes ✓ the instructions which are written in binary code, then it executes ✓ the instruction before starting the cycle all over again.

#### OR

The operating cycle of a CPU follows a 'fetch-decode-execute' cycle.

The operating cycle of a CPU follows a 'Input-Process-Output' cycle.

(3)

5.2.2 The CIR holds the instruction ✓ that is currently being executed ✓ at a specific address. ✓

#### OR

- The Current Instruction Register (CIR) splits the instruction into two parts.

- One part is decoded by the control unit ready for execution.

- The other part is the address of the data stored that needs to be used together with that instruction.

(3)

- 5.2.3 The ADC detects a continuously variable (analogue) signal and changes ✓ this analogue signal, ✓ without altering its essential content, into a multi-level (digital) signal. ✓

- (3)

- The timer is programmed to count to a predetermined number. ✓

- Data is fed into the CIR via the MDB in parallel. ✓

- The clock pulses together with the number being counted to determine the time duration. ✓

- When the 8-bit count finally overflows the register, an output signal is generated on the following clock pulse. ✓

- This could trigger an interrupt in the processor or set a bit that the processor can read. ✓

- Once done the register is cleared on the next clock pulse. ✓

#### $\mathsf{OR}$

The timer accepts data, one bit at a time, controlled by the pulse rate of the clock, incrementing (adding one by one) for each pulse until the register overflows.

(6)

# NSC – Marking Guidelines

| 5.3 | <ul> <li>The RAM stores all the data that is required to be processed by the CF during the execution of programmes. ✓</li> <li>OR</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                             |     |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|     |                                                                                                                                              | A can both read and write data into it.  an hold programmes, operating systems and data required by the                                                                                                                                                                                                                                                                                                                     | (1) |  |  |

| 5.4 | 5.4.1                                                                                                                                        | <ul> <li>Simplex ✓</li> <li>Duplex ✓</li> <li>Half-duplex</li> <li>Full-duplex</li> </ul>                                                                                                                                                                                                                                                                                                                                   | (2) |  |  |

|     | 5.4.2                                                                                                                                        | <ul> <li>Faster ✓</li> <li>Higher Bandwidth ✓ (More bits can be transferred in a shorter time)</li> </ul>                                                                                                                                                                                                                                                                                                                   | (2) |  |  |

|     | 5.4.3                                                                                                                                        | <ul> <li>The system needs a clock signal to both transmitter and receiver. ✓</li> <li>It operates on a primary/secondary configuration where one system (the transmitter) has control over the operation and the receiver is the secondary. ✓</li> <li>The systems need to be synchronised.</li> </ul>                                                                                                                      | (2) |  |  |

| 5.5 | <ul> <li>Tha</li> <li>as v</li> <li>Whi usin</li> <li>I<sup>2</sup>C wire</li> </ul>                                                         | Inter-integrated bus (I <sup>2</sup> C) is a powerful two wire bus ✓ That can support up to one thousand slave devices ✓ as well as supporting the communication of multiple masters ✓ Which, cannot talk to each other over the bus and have to take turns in using the bus lines. I <sup>2</sup> C uses start and stop sequences between masters and slaves over a two wire system. It works on a master-slave principle. |     |  |  |

| 5.6 | 5.6.1                                                                                                                                        | Master ✓                                                                                                                                                                                                                                                                                                                                                                                                                    | (1) |  |  |

|     | 5.6.2                                                                                                                                        | Serial Clock Line ✓                                                                                                                                                                                                                                                                                                                                                                                                         | (1) |  |  |

|     | 5.6.3                                                                                                                                        | Pull-up resistors, connected to a +5 V supply, are necessary for the lines (SCL and SDA) $\checkmark$ to go high. $\checkmark$                                                                                                                                                                                                                                                                                              | (2) |  |  |

|     | 5.6.4                                                                                                                                        | A slave cannot initiate a transfer over the l <sup>2</sup> C bus. ✓ A slave interprets instructions received by the master.                                                                                                                                                                                                                                                                                                 | (1) |  |  |

|     | 5.6.5                                                                                                                                        | <ul> <li>I<sup>2</sup>C requires only two wires ✓</li> <li>I<sup>2</sup>C supports multiple devices on the same bus without additional select lines ✓</li> <li>I<sup>2</sup>C ensures that data sent is received by the slave device. ✓</li> <li>I<sup>2</sup>C is cheaper to implement</li> <li>I<sup>2</sup>C supports multiple master devices</li> <li>I<sup>2</sup>C is less susceptible to noise than SPI</li> </ul>   | (3) |  |  |

| 5.7 | 5.7.1                                                                                                                                        | Logic '1' between -3 V and -25 V ✓<br>Logic '0' between +3 V and +25 V ✓                                                                                                                                                                                                                                                                                                                                                    | (2) |  |  |

# 15 NSC – Marking Guidelines

|     | 5.7.2 | <ul> <li>Used in low-data-rate short range applications such as;</li> <li>printers, ✓</li> <li>modems, ✓</li> <li>data projectors, ✓</li> </ul> | (0) |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |       | CNC machine tools                                                                                                                               | (3) |

| 5.8 | 5.8.1 | A program is a sequence of instructions ✓ that informs a computer how to perform a task. ✓                                                      | (2) |

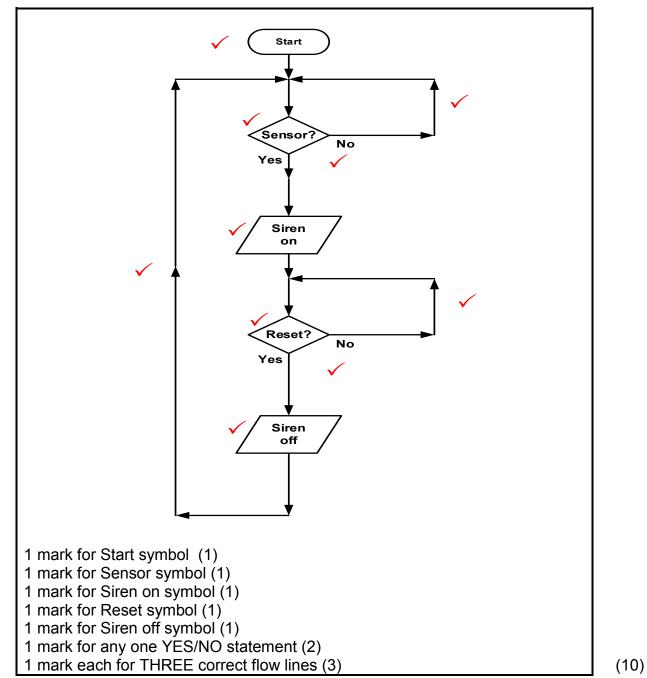

|     | 5.8.2 | A flow diagram is a visual representation of steps and decisions ✓ needed to perform and complete a process. ✓                                  | (2) |

**NOTE:** Each design must be assessed on merit and variations should be allowed.

**TOTAL: 200**

[55]